- Robotica - Automazione - Informatica

- Informatica industriale

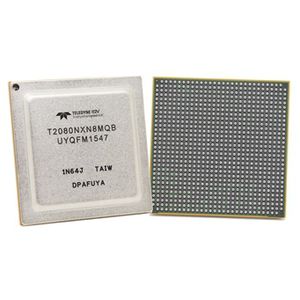

- Processore dual core

- e2v scientific instruments

Processore dual core PC8572E

Aggiungi ai preferiti

Confronta con altri prodotti

Caratteristiche

- Numero di core

- dual core

Descrizione

CARATTERISTICHE

- Dual Embedded e500 Cores, scalabilità fino a 1,5 GHz

- 6897 MIPS a 1500 MHz (stima di Dhrystone 2.1)

- Indirizzamento fisico a 36 bit

- Supporto avanzato per il debug dell'hardware e del software

- Unità a virgola mobile a doppia precisione

- Unità di gestione della memoria

- Cache L1/L2 integrata

- L1 Cache: Cache con 32 KB Data e 32 KB Instruction Cache con

Supporto per la chiusura di linea

- Shared L2 Cache: 1 MB con ECC

- Coerenza hardware L1 e L2

- L2 Configurabile come le transazioni SRAM, Cache e I/O possono

essere ospitati nelle regioni Cache L2

- Controllore di memoria DDR integrato con supporto ECC completo,

Sostenere:

- 333 MHz Clock Rate (667 MHz data rate), 64 bit, 1.8V

SSTL, DDR2 SDRAM

- 400 MHz Clock Rate (fino a 800 MHz Data Rate), 64 bit,

1.5V SSTL, DDR3 SDRAM

- Piattaforma di accelerazione delle applicazioni

- TLU avanzato

- Motore di sicurezza integrato che supporta DES, 3DES, MD-5,

SHA-1/2, AES, RSA, RSA, RNG, Kasumi F8/F9 e ARC-4

Algoritmi di crittografia

- PME integrato (espressione regolare)

- Sgonfiaggio dei pacchetti motore

- Motore di sicurezza integrato con XOR

- Quattro controller Ethernet a tripla velocità On-chip, a tripla velocità che supportano

Reti da 10 e 100 Mbps e 1 Gbps Ethernet/IEEE 802.3 Reti

con MII, RMII, GMII, GMII, SGMII, RGMII, RTBI e TBI Physical

Interfacce e IEEE 1588

- TCP/IP Checksum Accelerazione e QoS avanzato

Caratteristiche

- Controllo del flusso senza perdite

- I/O per uso generale

- Interconnessione seriale RapidIO e PCI Express Interconnessione ad alta velocità

Interfacce

- Tessuto per interruttori di rete on-chip (OCeaN)

- 133 MHz, 32 bit, 3,3V I/O, bus locale con memoria

Controllore

- Doppio controllore DMA integrato

- Doppio I

2

C e DUARTS

- Controllore di interrupt programmabile Controller

- Porta di accesso al test IEEE 1149.1 JTAG Test Access Port

- 1,1V Tensione di base con 3,3V/2,5V/1,8V I/O

- Pacchetto PBGA 1023-pin PBGA

---

Cataloghi

Nessun catalogo è disponibile per questo prodotto.

Vedi tutti i cataloghi di e2v scientific instrumentsAltri prodotti e2v scientific instruments

Semiconductors

* I prezzi non includono tasse, spese di consegna, dazi doganali, né eventuali costi d'installazione o di attivazione. I prezzi vengono proposti a titolo indicativo e possono subire modifiche in base al Paese, al prezzo stesso delle materie prime e al tasso di cambio.