Microcontrollore 32 bit ADSP-21567 seriesper applicazioni automobilistichedi uso generaleanalogico

Aggiungi ai preferiti

Confronta con altri prodotti

Vuoi acquistare direttamente?

Vai sul nostro Shop.

Caratteristiche

- Tipo

- 32 bit

- Applicazioni

- di uso generale, per applicazioni automobilistiche

- Altre caratteristiche

- analogico

Descrizione

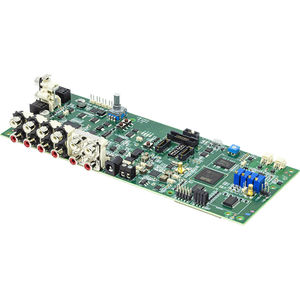

Infrastruttura del nucleo SHARC

Frequenza di clock del core a 600 MHz (max) o 800 MHz (max)

640KB di memoria SRAM di livello 1 (L1) on-chip (con parità) aumenta le prestazioni a bassa latenza

Supporto in virgola mobile a 32-bit, 40-bit e 64-bit

Punto fisso a 32 bit

Byte, parola corta, parola, parola lunga indirizzata

Memoria

512KB on-chip Livello 2 (L2) SRAM con protezione ECC - elimina la necessità di memoria esterna in molti casi d'uso

Un'interfaccia di livello 3 (L3) ottimizzata per la bassa potenza del sistema, che fornisce un'interfaccia a 16 bit per dispositivi SDRAM DDR3 (che supportano dispositivi DDR3L capaci di 1,35 V)

Controller di memoria DDR/DDR3L a 16 bit

1.Supporto a 35V per DDR3L

Acceleratori hardware avanzati

Motori FIR/IIR offload migliorati che funzionano alla frequenza di clock Core per una maggiore potenza di elaborazione

Motori crittografici di sicurezza con OTP

Potente sistema DMA

L'innovativa interfaccia audio digitale (DAI) include:

8x interfacce SPORT complete con modalità TDM e I2S

2x S/PDIF Rx/Tx, 8 coppie ASRC

4 generatori di clock di precisione

28 buffer

Altre connettività/interfacce periferiche:

2x Quad SPI, 1x Octal SPI

MLB 3-pin

6x I2C, 3x UARTs

2 porte di collegamento

10x timer per scopi generali, 1x contatore per scopi generali

2 timer watchdog

4-ch 12bit Housekeeping ADCs

40 pin GPIO, 28 pin DAI

Sensore termico

Pacchetto

17mm x 17mm (passo 0.8mm) 400-ball CSP_BGA

Sicurezza e protezione

Acceleratori hardware crittografici

Avvio rapido e sicuro con protezione IP

Acceleratori FIR e IIR migliorati che funzionano fino a 1 GHz

Qualificato AEC-Q100 per applicazioni automobilistiche

---

Cataloghi

Nessun catalogo è disponibile per questo prodotto.

Vedi tutti i cataloghi di ADIRicerche correlate

- Commutatore unipolare

- Amplificatore di segnale

- Ricetrasmettitore ADI

- Amplificatore di potenza

- Ricetrasmettitore Ethernet ADI

- Convertitore industriale

- Ricetrasmettitore di dati ADI

- Amplificatore elettronico

- Amplificatore digitale

- Amplificatore DC

- Amplificatore per strumentazione

- Amplificatore di tensione

- Convertitore di potenza

- Amplificatore analogico

- Amplificatore a basso rumore

- Amplificatore di corrente

- Amplificatore regolabile

- Ricetrasmettitore Ethernet gigabit

- Microcontrollore

- Amplificatore audio

* I prezzi non includono tasse, spese di consegna, dazi doganali, né eventuali costi d'installazione o di attivazione. I prezzi vengono proposti a titolo indicativo e possono subire modifiche in base al Paese, al prezzo stesso delle materie prime e al tasso di cambio.