- Robotica - Automazione - Informatica

- Informatica industriale

- Processore

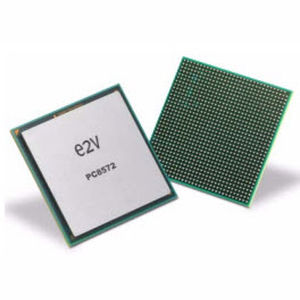

- e2v scientific instruments

Processore PC8548E

Aggiungi ai preferiti

Confronta con altri prodotti

Vuoi acquistare direttamente?

Vai sul nostro Shop.

Descrizione

CARATTERISTICHE

• E500 il centro incluso, offerti iniziali fino a 1,2 gigahertz

– Spedizione doppia Superscalar, progettazione della conduttura di 7 fasi con

edizione ed esecuzione guastate

– 3065 MIPS a 1333 megahertz (Dhrystone stimato 2,1)

• un indirizzo fisico di 36 bit

• L'hardware ed il software migliorati mettono a punto il supporto

• Scalare a precisione doppia e vettore inclusi di virgola mobile

APUs

• Unità della gestione della memoria (MMU)

• Nascondiglio integrato L1/L2

– Dati di KB di L1 Cache-32 e cache di istruzione di KB 32 con

Linea-chiusura del supporto a chiave

– KB di L2 Cache-512 (8-Way ha messo associativo); 512 KB/256

Il KB di KB/128 KB/64 può essere usato come SRAM

– Coerenza dell'hardware L1 e L2

– L2 configurabile come SRAM, il nascondiglio e transazioni dell'ingresso/uscita

Può essere messo in serboe nelle regioni del nascondiglio L2

• Supporto integrato di CEE di With Full del regolatore di memoria della RDT,

Appoggio:

– Una frequenza di clock di 200 megahertz (un tasso di 400 dati di megahertz), 64 bit,

2.5V/2.6V INGRESSO/USCITA, DDR SDRAM

• Motore integrato di sicurezza che sostiene DES, 3DES, MD-5,

SHA-1/2, AES, RSA, RNG, Kasumi F8/F9 e ARC-4

Algoritmi crittografici

• Quattro regolatori di Ethernet di Triplo-velocità del Su chip (GMACs)

Sostenendo 10 - e 100-Mbps e 1-Gbps

Ethernet/IEEE*802.3 reti con MII, RMII, GMII, RGMII,

Interfacce fisiche di TBI e di RTBI

– Accelerazione di totale di controllo del TCP/IP

– Caratteristiche avanzate di QoS

• Ingresso/uscita per tutti gli usi (GPIO)

• Interconnessione ad alta velocità di serie di PCI Express e di RapidIO

Interfacce, sostenenti

– Singolo x8 PCI Express, o singolo x4 PCI Express e

Singolo 4x RapidIO di serie

• tessuto del commutatore della rete del Su chip (oceano)

• Supporto multiplo dell'interfaccia del PCI

– ingresso/uscita 66 megahertz, 3.3V del regolatore del bus del PCI 2,2 di 64 bit (fino a)

– ingresso/uscita 133 megahertz, 3.3V del regolatore del bus di 64 bit PCI-X (fino a),

o flessibilità configurare due regolatori del PCI di 32 bit

• 166 megahertz, 32 bit, 3.3V ingresso/uscita, bus locale con la memoria

Regolatore

---

Cataloghi

Nessun catalogo è disponibile per questo prodotto.

Vedi tutti i cataloghi di e2v scientific instrumentsAltri prodotti e2v scientific instruments

Semiconductors

* I prezzi non includono tasse, spese di consegna, dazi doganali, né eventuali costi d'installazione o di attivazione. I prezzi vengono proposti a titolo indicativo e possono subire modifiche in base al Paese, al prezzo stesso delle materie prime e al tasso di cambio.