Software di gestione Xpedition Substrate Integratordi visualizzazionedi progettazionedi pianificazione

Aggiungi ai preferiti

Confronta con altri prodotti

Vuoi acquistare direttamente?

Vai sul nostro Shop.

Caratteristiche

- Funzione

- di gestione, di visualizzazione, di progettazione, di pianificazione, di ottimizzazione, di verifica, di connettività, per la realizzazione di prototipi

- Applicazioni

- di processo

- Tipo

- 3D

Descrizione

Pianificazione della connettività dei pacchetti IC 2,5/3D eterogenei e omogenei, prototipazione dell'assemblaggio e coottimizzazione della tecnologia di sistema.

2.pianificazione e prototipazione di pacchetti IC 5/3D

La prototipazione precoce e l'esplorazione consentono agli ingegneri di valutare diversi scenari di integrazione ASIC/chiplet, interposer, package e PCB al fine di soddisfare gli obiettivi complessivi di PPA, dimensioni del dispositivo, routabilità e costi prima dell'implementazione fisica dettagliata.

Caratteristiche principali di Substrate Integrator

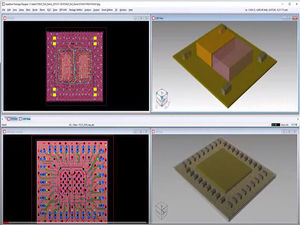

Importazione di schemi completi o parziali

La connettività logica dell'assemblaggio dei pacchetti IC può essere costruita utilizzando schemi grafici completi o parziali, utili per progetti con un numero elevato di dispositivi come i moduli SiP e/o per il riutilizzo/retargeting di progetti precedenti.

Gestione della connettività dei pacchetti a livello di sistema

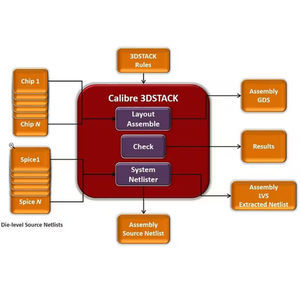

Gestione della connettività del sistema, visualizzazione e verifica logica a livello di sistema di progetti di pacchetti IC multi-die, multi-componente e multi-substrato.

Aggregazione di die, chipset e substrati

Xpedition Substrate Integrator integra die, chiplet e interposer provenienti da nodi di processo e fornitori diversi. Sono supportati diversi formati, tra cui LEF/DEF, GDS, AIF e CSV/TXT. I modelli virtuali gerarchici della matrice supportano le modifiche ECO bidirezionali degli oggetti in fase di progettazione/ottimizzazione.

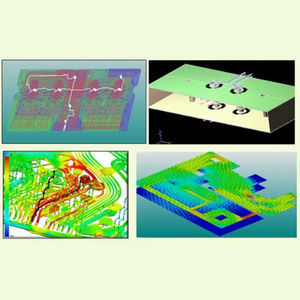

Co-ottimizzazione del substrato trasversale Silicon-package-PCB

La pianificazione e la co-ottimizzazione cross-substrate migliorano notevolmente la prevedibilità durante l'implementazione, individuando e risolvendo i problemi prima che diventino sorprese in fase avanzata. Una prospettiva di sistema con visibilità su più substrati migliora la comunicazione e il coordinamento grazie a un feedback immediato sulle decisioni prese in genere a livello di singolo substrato.

---

Cataloghi

Xpedition Substrate Integrator

4 Pagine

Ricerche correlate

- Soluzione software di automatizzazione

- Soluzione software di gestione

- Soluzione software di analisi

- Soluzione software di processo

- Soluzione software Windows

- Software CAD

- Soluzione software di regolazione

- Soluzione software in tempo reale

- Software in linea

- Soluzione software di progettazione

- Soluzione software 3D

- Software di interfaccia

- Software ad uso industriale

- Software di misura

- Software di qualità

- Software di simulazione

- Soluzione software di visualizzazione

- Software automatizzato

- Soluzione software di rete

- Soluzione software di sviluppo

* I prezzi non includono tasse, spese di consegna, dazi doganali, né eventuali costi d'installazione o di attivazione. I prezzi vengono proposti a titolo indicativo e possono subire modifiche in base al Paese, al prezzo stesso delle materie prime e al tasso di cambio.