Software di progettazione Simulink Design Verifier™diagnosticodi verifica

Aggiungi ai preferiti

Confronta con altri prodotti

Vuoi acquistare direttamente?

Vai sul nostro Shop.

Caratteristiche

- Funzione

- di progettazione, diagnostico, di verifica

Descrizione

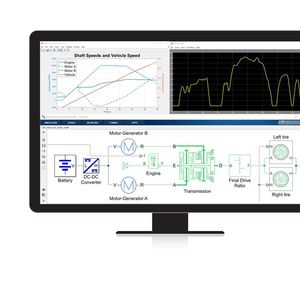

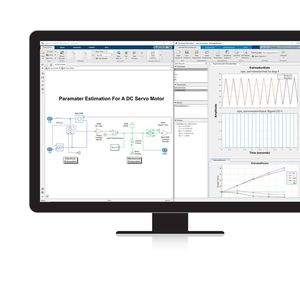

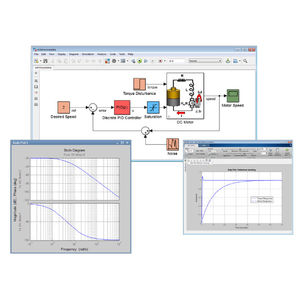

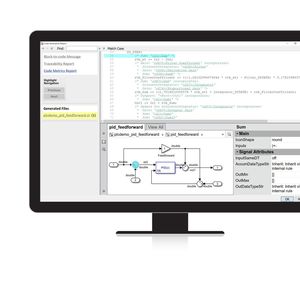

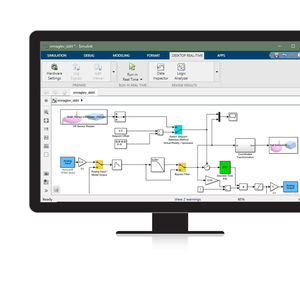

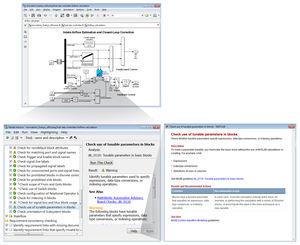

Simulink Design Verifier™ usa metodi formali per individuare errori di progettazione nascosti nei modelli. Rileva i blocchi del modello che presentano integer overflow, logica morta, violazioni di accesso agli array e divisioni per zero. Può verificare formalmente che il progetto risponda ai requisiti funzionali. Per ciascun errore di progettazione o violazione dei requisiti, genera un test case di simulazione per il debug.

Simulink Design Verifier genera test case per la e obiettivi personalizzati per ampliare i test case esistenti basati sui requisiti. Questi test case stimolano il tuo modello affinché soddisfi gli obiettivi di copertura di condition, decision, modified condition/decision (MCDC) e obiettivi di copertura personalizzati. Oltre agli obiettivi di copertura, è possibile specificare obiettivi di test personalizzati per generare in modo automatico test case basati sui requisiti.

Il supporto relativo agli standard industriali è disponibile nell’IEC Certification Kit (for ISO 26262 and IEC 61508) e nel DO Qualification Kit (for DO-178 and DO-254).

VIDEO

Cataloghi

Ricerche correlate

- Soluzione software di automatizzazione

- Soluzione software di gestione

- Soluzione software di analisi

- Soluzione software di processo

- Soluzione software Windows

- Software CAD

- Soluzione software di regolazione

- Soluzione software in tempo reale

- Software in linea

- Soluzione software di progettazione

- Soluzione software 3D

- Software di misura

- Software di simulazione

- Soluzione software di visualizzazione

- Software automatizzato

- Software di programmazione

- Soluzione software di rete

- Software di ingegneria

- Software di macchina

- Soluzione software per reportistica

* I prezzi non includono tasse, spese di consegna, dazi doganali, né eventuali costi d'installazione o di attivazione. I prezzi vengono proposti a titolo indicativo e possono subire modifiche in base al Paese, al prezzo stesso delle materie prime e al tasso di cambio.