- Elettricità - Elettronica

- Componente Elettronico

- GEB Enterprise

- Prodotti

- Cataloghi

- News & Trends

- Fiere

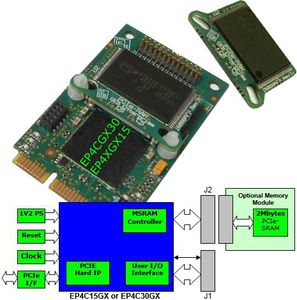

Porta PCI-EXPRESS GPIO-BUS MS64-Windows| 141030-01A1

Aggiungi ai preferiti

Confronta con altri prodotti

Vuoi acquistare direttamente?

Vai sul nostro Shop.

Descrizione

Il IP di IOBUS è un padrone asincrono dinamicamente reconfigurable del bus progettato tramite impresa di GEB. Sostiene lle interruzioni larghe e esterne del 8/16/32 di canale omnibus di dati, stato latente fisso o ciclo variabile del bus di stato latente.

Lo IOBUS sarà il bus utilizzato per la comunicazione fra un numero matrice (la carta di Pcie) e non specificato degli schiavi. Il bus sostiene fino a 32 bit di dati, un indirizzo dei fino a 8 bit, il circuito integrato 2 prescelto (CS#), indicato permette a (RD#), scrive la richiesta dello stroboscopio (WR#), di interruzione (INT#) e un segnale facoltativo di attesa (WAIT#).

Dal lato interno del bus, il IP di IOBUS è in pieno soddisfacente rispetto alla specifica di Altera Avalon, in modo da può aggiungersi facilmente a tutto il disegno di Altera Qsys. Da questo lato, ci è interfaccia dello schiavo di due Avalon, quella prima è identificato MEM permette i acces ai dispositivi esterni. La seconda interfaccia è identificata CSR, esso realizza i registri dello spazio di configurazione che devono essere utilizzati a programmare le sincronizzazioni. Il CSR permette selettivamente la programmazione della messa a punto (st), larghezza di impulso (tpw), tempo di stretta (Th) per colto e scrive i cicli ed anche l'utente può anche permettere sia alla richiesta di interruzione che i segnali di attesa e la loro polarità.

---

* I prezzi non includono tasse, spese di consegna, dazi doganali, né eventuali costi d'installazione o di attivazione. I prezzi vengono proposti a titolo indicativo e possono subire modifiche in base al Paese, al prezzo stesso delle materie prime e al tasso di cambio.